Протокол V.32bis

Протокол модуляции V.32bis был разработан с целью обеспечения передачи данных со скоростью до 14400 бит/с по двухпроводным коммутируемым и выделенным телефонным каналам. Этот протокол был принят в качестве стандарта ITU-Т в 1991 году. Основные характеристики модемов, поддерживающих этот протокол, представлены ниже:

- Дуплексный режим работы по коммутируемым каналам телефонных сетей общего пользования и арендуемым двухпроводным линиям передачи;

- Реализация эхоподавления;

- Применение КАМ при скорости модуляции 2400 Бод;

- Частота несущей равна 1800 Гц;

- Приемник модема обеспечивает работу при нестабильности частоты принимаемого сигнала в пределах ±7 Гц;

- Скорости передачи данных: 14400, 1200, 9600, 7200 бит/с с треллис-кодированием и 4800 бит/с без кодирования;

- Совместимость с модемами V.32 на скоростях 9600 и 4800 бит/с;

- Обмен управляющими последовательностями и выбор скорости передачи в процессе установления связи;

- Возможность смены скорости передачи во время сеанса связи без разрыва соединения;

- Асимметричный режим передачи не поддерживается, то есть скорости передачи и приема каждого модема должны быть одинаковыми;

- Спектр сигнала ограничен полосой частот от 600 Гц до 3000 Гц.

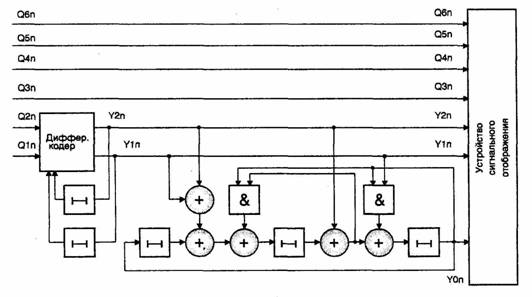

Рис. 6.17. Схема кодирования информации в модеме V.32bis

Таблица 6.2 описывает правило дифференциального кодирования при использовании сигнально-кодовой конструкции.

| Вход | Предыдущий выход | Выход | |||

| Q1n | Q2n | Y1n-1 | Y2n-1 | Y1n | Y2n |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 |

Два первых бита Qln и Q2n в каждом блоке при любой скорости передачи (индекс n обозначает порядковый номер блока информационной последовательности) поступают на дифференциальный кодер, где они перекодируются в биты Y1n и Y2n согласно таблице 6.2.

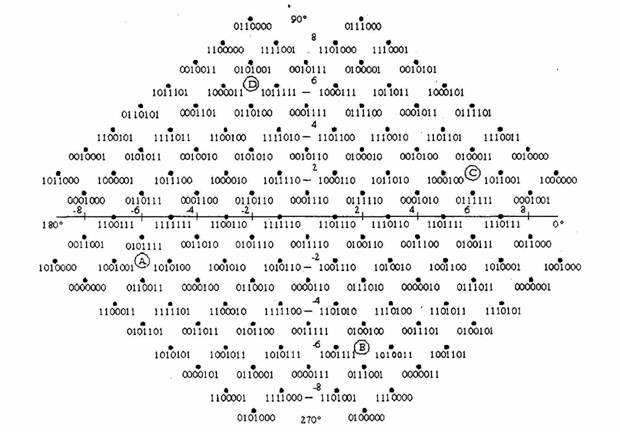

Дифференциальные биты Y1n и Y2n используются в качестве входных для систематического сверточного кодера, который генерирует избыточный бит YOn. Этот избыточный бит и шесть информационных бит Y1n, Y2n, Q3n, Q4n, Q5n, Q6n поступают на устройство сигнального отображения, которое формирует элементы сигнального созвездия, представленного на рис. 6.18. Двоичные числа на рис. 6.18 соответствуют последовательности битов YOn, Y1n, Y2n, Q3n, Q4n, Q5n, Q6n, а обозначения А, В, С, D — синхронизирующим сигнальным элементам.

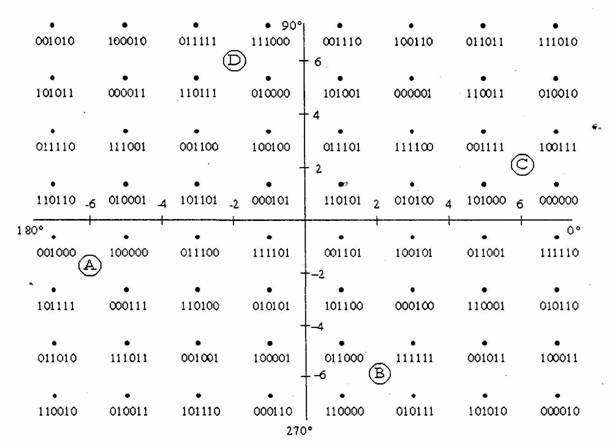

На скорости передачи 12000 бит/с входной проскремблированный поток данных делится на группы по пять бит. Процесс дифференциального кодирования и кодирования сверточным кодом принципиально ничем не отличается от кодирования при скорости 14400 бит/с. При скорости 12000 бит/с формируются элементы сигнального созвездия, приведенного на рис. 6.19. Двоичные числа на рис. 6.19 соответствуют последовательности шести битов YOn, Y1n, Y2n, Q3n, Q4n, Q5n, а обозначения А, В, С, D, как и ранее, соответствуют синхронизирующим сигнальным элементам.

Рис. 6.18. Сигнальная диаграмма для скорости 14400 бит/с

При скорости передачи 9600 бит/с входной проскремблированный поток данных делится на блоки по четыре бита Q1n, Q2n, Q3n, Q4n. В результате этого схема кодера V.32bis при скорости 9600 бит/с соответствует кодеру V.32. Пространственная сигнальная диаграмма соответствует диаграмме модемов V.32 при той же скорости передачи (рис. 6.16). Двоичные числа на диаграмме соответствуют последовательности пяти битов YOn, Y1n, Y2n, Q3n, Q4n, поступающих на вход устройства сигнального отображения.

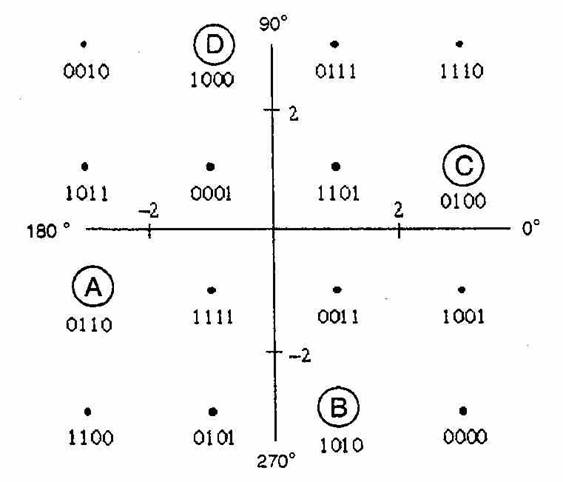

При скорости передачи 7200 бит/с входной проскремблированный поток данных делится на блоки по три бита Q1n, Q2n, Q3n. Пространственная сигнальная диаграмма для этой скорости передачи представлена на рис. 6.20. В этом случае двоичные числа соответствуют последовательности четырех бит YOn, Y1n, Y2n, Q3n, поступающих на вход устройства сигнального отображения.

При скорости 4800 бит/с скремблированный входной поток данных делится на блоки по два бита Q1n и Q2n, которые поступают на вход дифференциального кодера, работающего согласно таблице 6.3.

С выхода дифференциального кодера биты Y1n и Y2n отображаются в передаваемые сигнальные элементы согласно диаграмме, представленной на рис. 6.14. Таким образом, при скорости 4800 бит/с кодирование избыточным сверточным кодом не производится.

Рис. 6.19. Сигнальная диаграмма для скорости 12000 бит/с

Двоичные числа на рис. 6.14 соответствуют последовательности двух бит Y1n и Y2n, поступающих на вход устройства сигнального отображения.

Рис. 6.20. Сигнальная диаграмма для скорости 7200 бит/с

Таблица 6.3. Правило дифференциального кодирования при скорости передачи 4800 бит/с

| Вход | Предыдущий выход | Изменение фазы | Выход | Сигнальная точка для 4800 бит/с | |||

| Q1n | Q2n | Y1n-1 | Y2n-1 | Y1n | Y2n | ||

| 0 | 0 | 0 | 0 | +90° | 0 | 1 | В |

| 0 | 0 | 0 | 1 | 1 | 1 | С | |

| 0 | 0 | 1 | 0 | 0 | 0 | А | |

| 0 | 0 | 1 | 1 | 1 | 0 | D | |

| 0 | 1 | 0 | 0 | 0° | 0 | 0 | А |

| 0 | 1 | 0 | 1 | 0 | 1 | В | |

| 0 | 1 | 1 | 0 | 1 | 0 | D | |

| 0 | 1 | 1 | 1 | 1 | 1 | С | |

| 1 | 0 | 0 | 0 | +180° | 1 | 1 | С |

| 1 | 0 | 0 | 1 | 1 | 0 | D | |

| 1 | 0 | 1 | 0 | 0 | 1 | В | |

| 1 | 0 | 1 | 1 | 0 | 0 | А | |

| 1 | 1 | 0 | 0 | +270° | 1 | 0 | D |

| 1 | 1 | 0 | 1 | 0 | 0 | А | |

| 1 | 1 | 1 | 0 | 1 | 1 | С | |

| 1 | 1 | 1 | 1 | 0 | 1 | В | |

Согласно протокола V.32bis, модемы должны иметь два самосинхронизирующихся скремблера. В каждом направлении передачи используется свой скремблер. Вызывающий модем использует скремблер с образующим полиномом 1+x^x^23, а отвечающий модем пользуется скремблером с образующим полиномом 1+x^x^23.